Hoplite is a configurable, general purpose, FPGA-optimal 2D router and tools for implementation of efficient network on chip (NOC) interconnection of diverse processors, accelerators, other client cores, and extreme bandwidth (100+ Gb/s) interfaces.

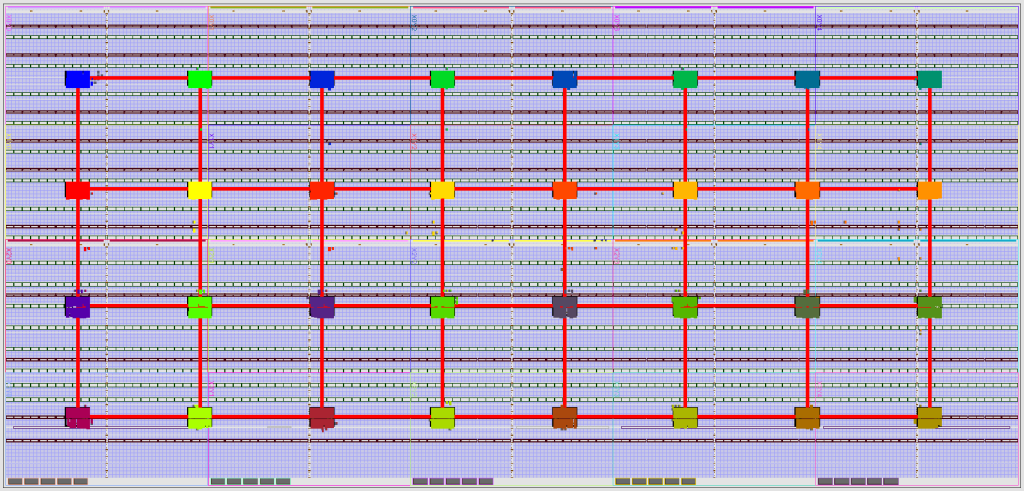

An example of a floorplanned 8Rx4C Hoplite NOC with 128b links. (Image rotated.) Clock period is 3 ns. Each link has a bandwidth of 43 Gb/s. This consumes just 2% of the LUTs of a Xilinx Kintex UltraScale KU040. The average no load latency from any router to a random destination router is 18 ns (6 cycles). In this layout, routers are explicitly placed into dense tiles and the torus is folded, i.e. routers of a similar color are directly connected.

UPDATE Gray Research LLC will soon offer a Hoplite Kit, comprising Verilog RTL source, documentation, and software tools including layout tools and NOC simulator, hosted on github. To be notified of availability, please register your interest via email.

Publications

Hoplite: Building Austere Overlay NoCs for FPGAs, Nachiket Kapre, Jan Gray.

25th International Conference on Field-Programmable Logic and Applications, Sept. 2015. Received the Michael Servit Best Paper Award. [PDF]

UPDATE: An expanded and updated version of this paper appeared in ACM Transactions on Reconfigurable Technology and Systems, 2017. Hoplite: A Deflection-Routed Directional Torus NoC for FPGAs [PDF].