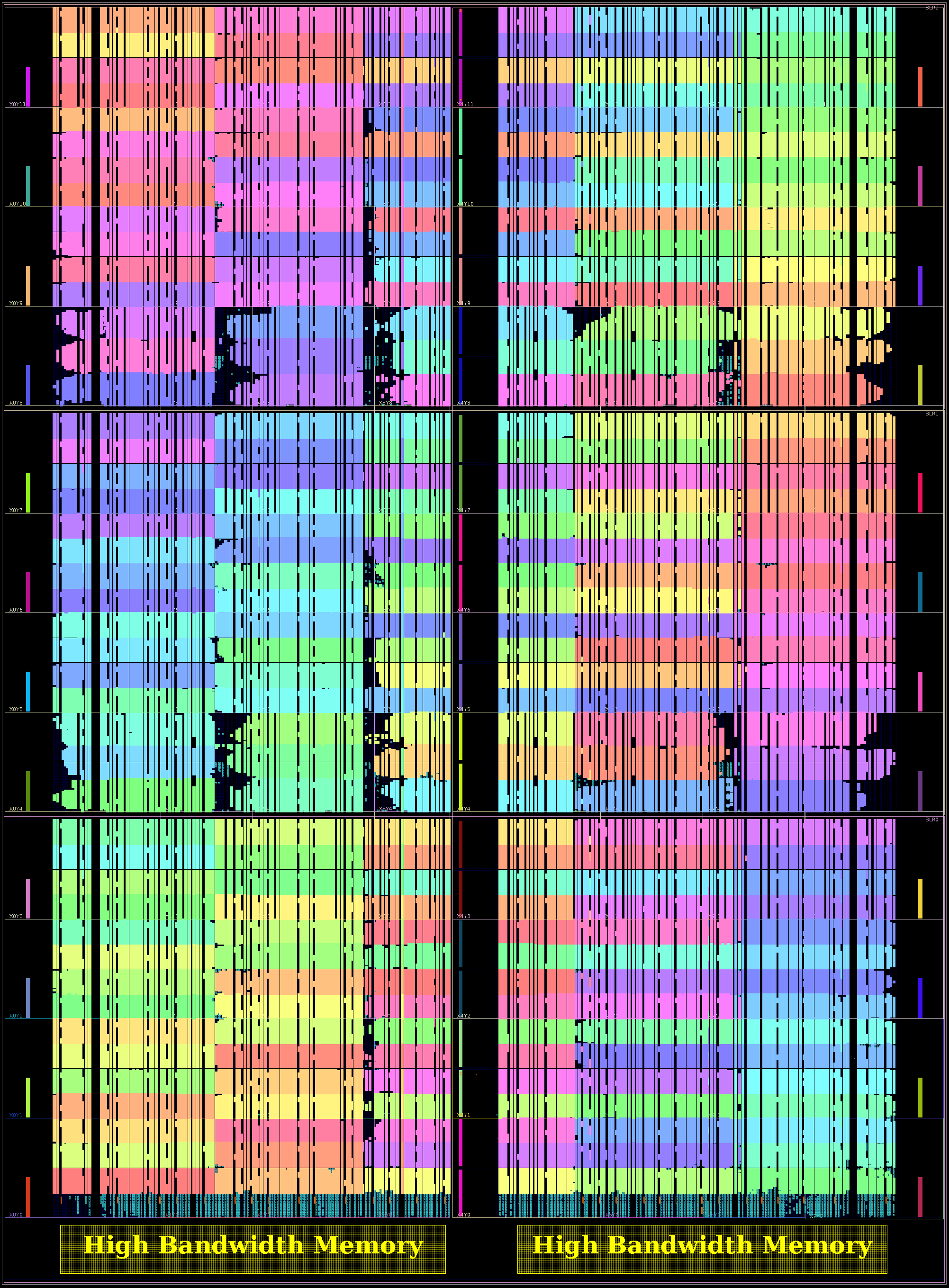

A device view (die plot) of an 1800 RISC-V PE implementation of the GRVI Phalanx massively parallel accelerator framework. 15×15 clusters of { 8 PE, 128 KB SRAM, and a 300b Hoplite NoC router }.

FPGA CPU News

Exploring Parallel Computer Architecture with FPGAs